我會以我自己的板子(Samsung S344b0),來針對內容做說明

A.記憶体控制

1.記憶体控制器暫存器

其中STn:代表其區塊n是否使用UB/LB(upper byte/Low byte)接腳,而UB/LB是在SRAM才會用到的。

nBE= nWBE and nOE。ST=0 ,pin[14:11]=nWBE; ST=1 ,pin[14:11]=nBE

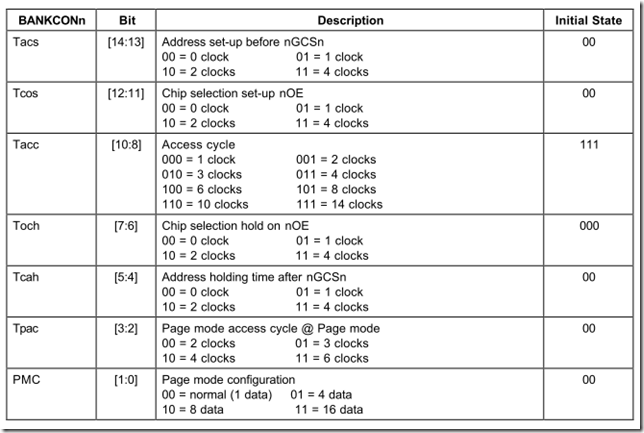

SROM 記憶体控制器暫存器

主要是設定區塊0-5的時序,以其page mode及no page mode下去設定

其中Tpac and PMC為分頁mode。

SDRAM(port 6,7)

==================================

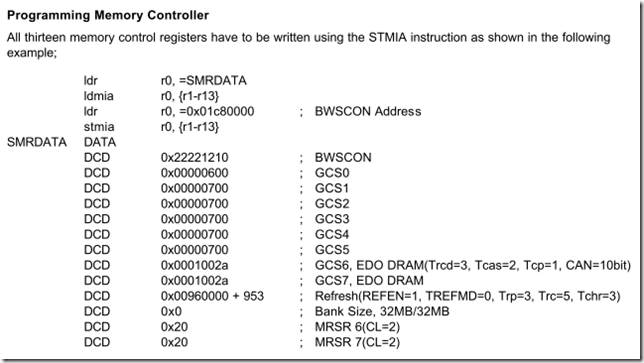

SMRDATA DATA

;*****************************************************************

; Memory configuration has to be optimized for best performance *

; The following parameter is not optimized. *

;*****************************************************************

;*** memory access cycle parameter strategy ***

; 1) Even FP-DRAM, EDO setting has more late fetch point by half-clock

; 2) The memory settings,here, are made the safe parameters even at 66Mhz.

; 3) FP-DRAM Parameters:tRCD=3 for tRAC, tcas=2 for pad delay, tcp=2 for bus load.

; 4) DRAM refresh rate is for 40Mhz.

在我的板子上,系統記憶体分配為

;bank0 16bit BOOT ROM SST39VF160/SST39VF320

;bank1 8bit Nand Flash K9F2808U0A/K9F5608U0A

;bank2 16bit USB1.1 PDIUSBD12

;bank3 RTL8019

;bank4 No Uesed

;bank5 No Uesed

;bank6 16bit SDRAM

;bank7 16bit SDRAM

//書出其bit mapping,

//設定BWSCON,條件編輯,1:16; 0 :8

[ BUSWIDTH=16

; DCD 0x11111111 ;Bank0=OM[1:0], Bank0~Bank7=16bit

DCD 0x11111001 ;Bank0=OM[1:0] 16bit BootRomSST39VF160/SST39VF320) :0x0

; |||||||- Bank1=8bit Nand Flash

; |||||--- Bank2=8bit PDIUSBD12

; ||||---- Bank3=16bit RTL8019

; |||----- Bank4~5=16bit No Uesd

; -------- Bank6~7=16bit SDRAM

| ;BUSWIDTH=32

DCD 0x22222220 ;Bank0=OM[1:0], Bank1~Bank7=32bit

]

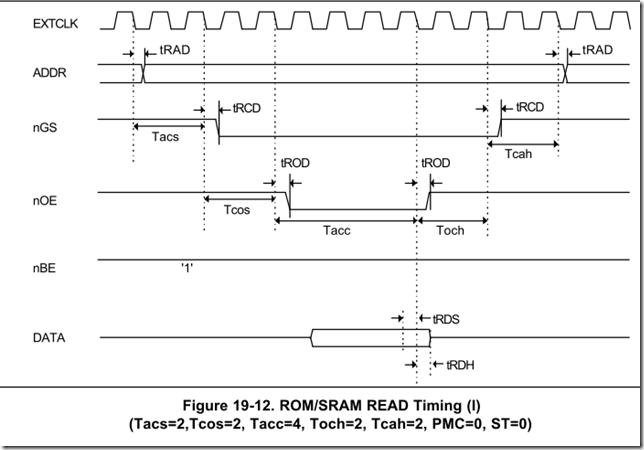

目標晶片讀取時序和我們的flash

設我們的ARM為66MHz(15ns)MCLK,後出晶片時序和Flash中定義比父

Flash參數名稱 S3C44B0參數名稱 S3c44B0速度 BankCon0對塵值

----------------------------------------------------------------------------------------------------------------

Tacc-Tce Tacs

20-120 0/15 0

----------------------------------------------------------------------------------------------------------------

none Tcos none 0

----------------------------------------------------------------------------------------------------------------

Trc-Tacc+toe Tacc

120-70+50 100/15=7 101?

----------------------------------------------------------------------------------------------------------------

……………

----------------------------------------------------------------------------------------------------------------

B0_Tacs EQU 0x0 ;0clk

B0_Tcos EQU 0x0 ;0clk

B0_Tacc EQU 0x6 ;10clk

B0_Tcoh EQU 0x0 ;0clk

B0_Tah EQU 0x0 ;0clk

B0_Tacp EQU 0x0 ;0clk

B0_PMC EQU 0x0 ;normal(1data)

//設定BANKCON0-7

//Bank 0

DCD ((B0_Tacs<<13)+(B0_Tcos<<11)+(B0_Tacc<<8) +(B0_Tcoh<<6)+(B0_Tah<<4)+(B0_Tacp<<2)+(B0_PMC)) ;GCS0

//Bank 1

DCD ((B1_Tacs<<13)+(B1_Tcos<<11)+(B1_Tacc<<8)+(B1_Tcoh<<6)+(B1_Tah<<4)+(B1_Tacp<<2)+(B1_PMC)) ;GCS1

//Bank 2

DCD ((B2_Tacs<<13)+(B2_Tcos<<11)+(B2_Tacc<<8)+(B2_Tcoh<<6)+(B2_Tah<<4)+(B2_Tacp<<2)+(B2_PMC)) ;GCS2

//Bank 3

DCD ((B3_Tacs<<13)+(B3_Tcos<<11)+(B3_Tacc<<8)+(B3_Tcoh<<6)+(B3_Tah<<4)+(B3_Tacp<<2)+(B3_PMC)) ;GCS3

//Bank 4

DCD ((B4_Tacs<<13)+(B4_Tcos<<11)+(B4_Tacc<<8)+(B4_Tcoh<<6)+(B4_Tah<<4)+(B4_Tacp<<2)+(B4_PMC)) ;GCS4

//Bank 5

DCD ((B5_Tacs<<13)+(B5_Tcos<<11)+(B5_Tacc<<8)+(B5_Tcoh<<6)+(B5_Tah<<4)+(B5_Tacp<<2)+(B5_PMC)) ;GCS5

設定RAS到CAS及其它

//SDRAM,or DRAM

[ BDRAMTYPE="DRAM"

DCD ((B6_MT<<15)+(B6_Trcd<<4)+(B6_Tcas<<3)+(B6_Tcp<<2)+(B6_CAN)) ;GCS6 check the MT value in parameter.a

DCD ((B7_MT<<15)+(B7_Trcd<<4)+(B7_Tcas<<3)+(B7_Tcp<<2)+(B7_CAN)) ;GCS7

| ;"SDRAM"

DCD ((B6_MT<<15)+(B6_Trcd<<2)+(B6_SCAN)) ;GCS6

DCD ((B7_MT<<15)+(B7_Trcd<<2)+(B7_SCAN)) ;GCS7

]

-------------------------------------------------------------------------------------------------------

;Bank 7 parameter

[ BDRAMTYPE="DRAM" ;MT=01(FP DRAM) or 10(EDO DRAM)

B7_MT EQU 0x2 ;EDO DRAM

B7_Trcd EQU 0x1 ;2clk

B7_Tcas EQU 0x1 ;2clk

B7_Tcp EQU 0x1 ;2clk

B7_CAN EQU 0x2 ;10bit

| ;"SDRAM" ;MT=11(SDRAM)

B7_MT EQU 0x3 ;SDRAM

B7_Trcd EQU 0x0 ;2clk

B7_SCAN EQU 0x0 ;8bit

]

----------------------------------------------------------------------------------------------------

;REFRESH parameter

REFEN EQU 0x1 ;Refresh enable

TREFMD EQU 0x0 ;CBR(CAS before RAS)/Auto refresh

Trp EQU 0x2 ;2clk 0x1 ;3clk --zq

Trc EQU 0x1 ;5clk

Tchr EQU 0x2 ;3clk

REFCNT EQU 1425 ;1019 ;period=15.6us, MCLK=40Mhz

;************************************************

END

//Refresh

DCD ((REFEN<<23)+(TREFMD<<22)+(Trp<<20)+(Trc<<18)+(Tchr<<16)+REFCNT) ;REFRESH RFEN=1, TREFMD=0, trp=3clk, trc=5clk,

//auto reflash

tchr=3clk,count=1019

DCD 0x07 ;SCLK power down mode, BANKSIZE 32M/32M

DCD 0x20 ;MRSR6 CL=2clk

DCD 0x20 ;MRSR7

****************************************************

;設定記憶體控制暫存器 *

;****************************************************

adr r0, ResetHandler

ldr r1, =ResetHandler

sub r0, r1, r0

ldr r1, =SMRDATA

sub r0, r1, r0

ldmia r0, {r1-r13}

ldr r0, =0x01c80000 ;BWSCON Address

stmia r0, {r1-r13}

沒有留言:

張貼留言