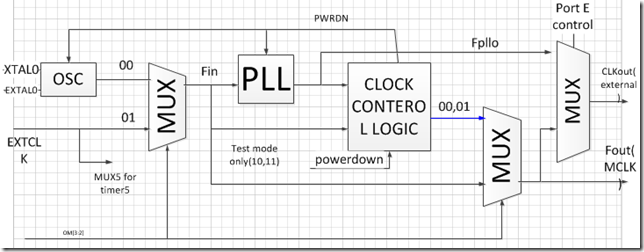

目標晶片可以產生時脈(clock),提供給CPU及周邊電路所用,稱為時脈產生器(clock generator),可以由軟体來擯制,來達成節電源使用量,基於上述的原理,目標晶片有多種電源管理模式來保持最佳的電源使用。

其晶片的電源管理模式有:

- normal mode :提供cpu及其它周邊所需之時脈,當電路運作時其功率最高,但也可藉由特殊register將不使用的週邊停止(如timer and DMA)

- slow mode:又稱非相位鎖相迴模式(non-pll mode),此模式下其cpu時脈由外部提供,其消耗電力由外部決定.

- idle mode:可停止cpu的時脈,但對其它週邊還是有供應。並且周邊發出的中斷,均可中止此一模式.

- stop mode:會停止相位鎖相迴路(PLL)來停止cpu及所有周邊電路時脈,此時只會有最小電流(10uA)。可由"外部中斷"來終止此模式.

- Sl idle mode:也是停止cpu,及除了LCD外的所有周邊,它會小於idle mode.

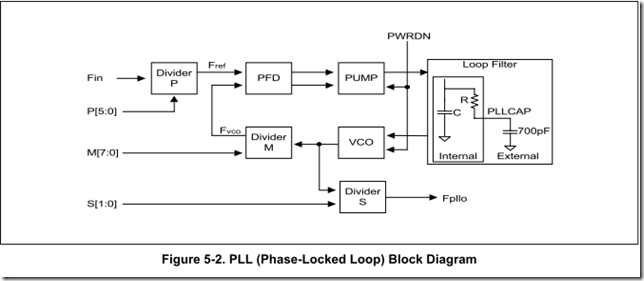

PLL(相位鎖相迴路,PLL(phase-Locked-loop)

功用:參考外部的頻率,及相位而產生輸出頻率的時脈產生器。

VCO產生與輸入DC電源相同比例的輸出頻率。

除法器P可將輸入frequence(FIN)除p,成為phase frequency detector,PFD)

除法器M可將VCO的輸出除m,成為相位頻率檢測器的輸入.

除法S可將VCO的輸出頻率除以S,成為PLL的輸出Fpllo.

Clock Control Logic(时脈控制)

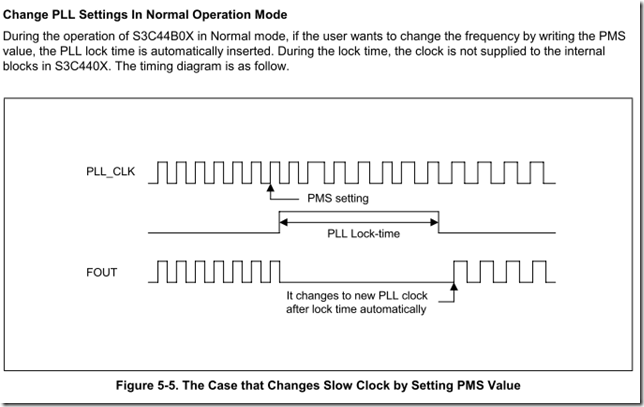

可由PLL的輸出或是外部振盪器,當PLL的輸出被重新設定時其clock generator logic會先停止Fout,直到PLLout隱定才會輸出Fout。此clock generator logic會在系統reset, power-down mode時啓動.

相位鎖相迴路的鎖定時間

(lock time),其PLLout的穩定時間,此時間至少需大屬208uS。而其Pllout的穩定時間,在reset,slow mode,stop mode.

鎖定時間與暫存器關於 (LOCKTIME) t_lock(PLL lock time)=(1/Fin) xn ; n=LTIMECNT(LOCKTIME register)

電源重置

power -on reset時其PLL動作

- Oscillator開始動作

- Oscillator穩定後,nReset會成高電位

- PLL用default動作.

- 此時PLLout並不隱定,所以Fin會取代Fpllo到Fout

- 在使用者未將新值寫入PLLCONtbln ,Fout的輸出直接與Fin連接,即使是使用預設也需要手動寫入一次

- 當PLLCON暫存器寫入後,需經"鎖定時間"才把Fpllo輸出。

一般模式下改變PLL

電源管理

其電源管理和PLL及clock generator logic、周邊電路的控制、及Wake-up 有關。

其晶片中有五種mode,而其之間的切換並不是可相互換。有一定的切換方式。

- normal mode:週邊電路、及基本(CPU,bus controller,memory controller,interrupt controller and power manage controller)。但可由軟体來設定電源暫存器來達到停正某一周邊電路.

- idle mode:只有cpu 會停止,其它還是正常。若要脫離則由外部中斷(EINT[7:0]、即時時鐘時脈警告中斷、其它中斷.

- stop mode:所有時脈都會停止,此時功率最低。當外部中斷(EINT[7:0]、即時時鐘時脈警告中斷、其它中斷 ,後會進入THAW mode,再跳到Normal mode. 而其Stop mode則需由Slow mode才能進入。

- 若由其它mode,到Stop 需經

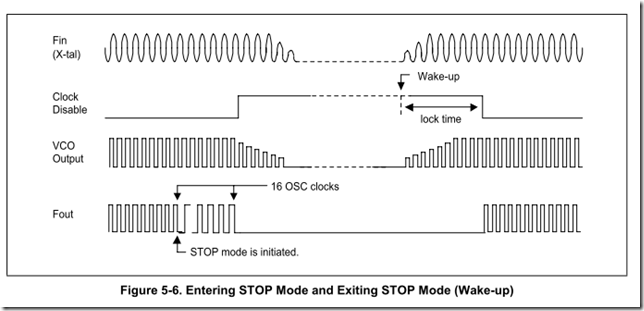

- 進入停止mode step

- clock controll logic會用Fin 取代 Fpllo,仍會有持續16次的Fin clock.

- 當Fin 持續16次後,Fout會停止輸出,然後進入停止mode.

- 所以進入stop mode所需時間為, 外部時脈的 X16

- Exit stop mode

- 產生外部中斷(EINT[7:0]、即時時鐘時脈警告中斷、其它中斷

- 挀盪器及PLL 開始,需鎖定時間延遲來保證Fout隱定。

- 在鎖定時間的延遲內Fout不會有輸出,當Fout隱定(經鎖定時間)才輸出Fout,脫離stop mode.

- 進入停止mode step

進入停止模式前使用者需

- DRAM/SDRAM必須進入Self-refresh

- LCD必須停止運作

- port需正確設定

- 先進slow mode,前其PLL仍工作正常。進入slow mode时才會 stop PLL.

- 進入slow mode前需要有一段延遲時間,在進入slow mode後的前3 clock前不可wake up,不然會無法離開slow mode。故需先 中斷停止一段時間。

- 當晶片進入停止mode後,MCLK應會高於Fin的2.5倍。當從停止模式下被喚醒至normal mode,主顏可由改變PLLCON改變。

- 若以 晶片由外部中斷EINT進入stop mode,則外部中斷是無法再由EINT 來喚醒。

慢速空轉模式

slow mode(SL_IDLE,S_LCD mode),系統中只有LCD work.其它 un work.

進入空轉模式step

- 在進入idle mode前,需先進入slow mode,且PLL必須先 disable.

- DRAM/SDRAM set self-refresh

- 0x46(enable LCD, idle mode、slow mode)寫入CLKCON 來進入slow mode

Exit idle mode

- 外訲中斷,即時時鐘時脈警告中斷

- 中斷產生後,CPU會進入slow mode

- 等待鎖定時間 end

- 鎖定時間 end結束後,清除SL_IDLE bit

慢冲模式

Slow mode、non-PLL mode,由使用低頻及停止PLL。Fout=Fin/CLKSLOW(SLOW_VAL)得。

脫離時(進入normal mode),則需一段定時間(400us)使其隱定。而在PLL on後,由CLKSLOW中的SLOW mode bit改變操作模式時脈。

在鎖定時間後,利用CLKSLOW中的SLOW mode bit脫離slow mode 進入norde,其頻率會在其slow mode解除時輸出.

在slow mode時同時改變CLKSLOW中的slow mode bit(Disable)及PLL(off),頻率會在鎖定時間後改變。

Wake-up and THAW

由Stop mode時,當由外部中斷或即時..中斷 wake-up 會先到THAWl ,此時CLKCON會被忽略,因為它是在stop mode時設定.

idle mode and stop mode:

1.設定PCONG,設EINT為input

2.EINTn為可中斷

電源管理時:

- entry idle mode

- CLKCON 's bit 2 set 1, delay some time

- PLL on/off

- 只有在slow mode turen off,其它則不可

- 由slow mode到其它mode,則需把PLL on,等PLL穩定後,再clear SLOW_BIT

- PUPS register and stop or idle mode

- I/O 接pull-high

- data bus pull-high

- PUPS and PUPD set data bus 31-16,

- PUPS reg set data bus 15-0

- PUPC,PUPD’PUPS

- outport stat and stop or idle

- output port 在high level ,省電

- ADC,

- set ADCCON

相關

PLLCON

CLKCON

CLKSLOW

LOCKTIME

沒有留言:

張貼留言