因為,我的modesim 都無法使用。

故我改由使用icrus verilog做為編譯+Gtkwave(波形)

而其軟体的使用上有一定的順序。

一、準備程式及testbench file

simple.v

simple_tb.v

二、

確定安裝好iverilog compiler及gtkwave(見參考)

三、

在生成*.vcd file時,需要經過三個步驟。並印出其所產生的template file

A. iverilog simple.v simple_tb.v -o tb.vvp

B. vvp tb.vvp (執行內容testbench內容)

simple.vcd是經由執行testbench內容所生成的。

C. gtkwave simple.vcd&

參考:

ICARUS VERILOG的使用

http://www.cnblogs.com/zhuangzhuang1988/archive/2012/03/30/2425052.html

http://www.wretch.cc/blog/henry0714/11669422

Icarus Verilog軟體安裝及使用

http://140.116.72.67/logic/Icarus_Verilog.pdf

http://www.ptt.cc/bbs/Electronics/M.1251620125.A.3D1.html

http://www.wretch.cc/blog/henry0714/11669422

https://sites.google.com/site/verilog710/xiang-guan-gong-ju/icarus-verilog

http://darkblack01.blogspot.tw/2012/10/iverilog-gtkwave-notepadverilog.html

故我改由使用icrus verilog做為編譯+Gtkwave(波形)

而其軟体的使用上有一定的順序。

一、準備程式及testbench file

simple.v

1: module simple(A, B,CIN,COUT,SUM);2:3: input A,B,CIN;4: output COUT,SUM;5: parameter delay=100;6:7: assign #delay {COUT,SUM}=A+B+CIN;8:9: endmodule

simple_tb.v

1: module simple_tb;2:3: reg A,B,CIN;4:5: wire COUT,SUM;6:7: initial8: begin9: $dumpfile("simple.vcd");10: $dumpvars(0, s);11: $monitor("A = %b, B = %b CIN = %b | COUT = %b SUM = %b ", A, B,CIN,COUT,SUM);12: #50 A = 1'b0; B=1'b0;CIN=1'b0;13: #50 A = 1'b0; B=1'b1;CIN=1'b0;14: #50 A = 1'b1; B=1'b0;CIN=1'b0;15: #50 A = 1'b1; B=1'b1;CIN=1'b0;16: #50 A = 1'b0; B=1'b0;CIN=1'b1;17: #50 A = 1'b0; B=1'b1;CIN=1'b1;18: #50 A = 1'b1; B=1'b0;CIN=1'b1;19: #50 A = 1'b1; B=1'b1;CIN=1'b1;20: #50 $finish;21: end22:23: simple #(30) s(A, B,CIN,COUT,SUM);24:25: endmodule

二、

確定安裝好iverilog compiler及gtkwave(見參考)

三、

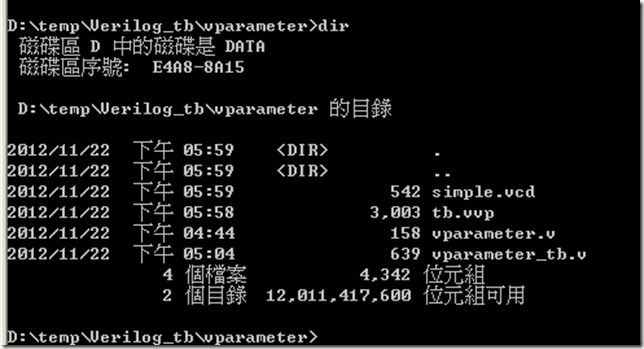

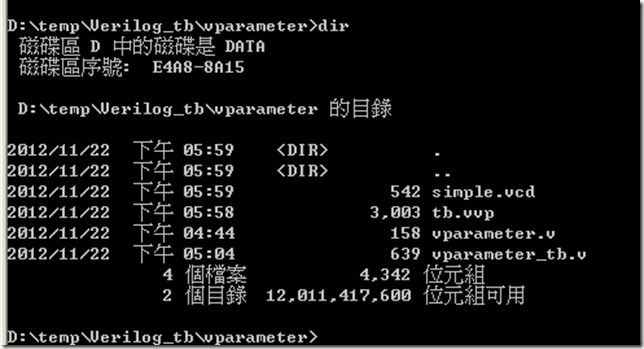

在生成*.vcd file時,需要經過三個步驟。並印出其所產生的template file

A. iverilog simple.v simple_tb.v -o tb.vvp

B. vvp tb.vvp (執行內容testbench內容)

simple.vcd是經由執行testbench內容所生成的。

C. gtkwave simple.vcd&

參考:

ICARUS VERILOG的使用

http://www.cnblogs.com/zhuangzhuang1988/archive/2012/03/30/2425052.html

Windows平台下使用開放軟件寫verilog

http://www.wretch.cc/blog/henry0714/11669422

Icarus Verilog軟體安裝及使用

http://140.116.72.67/logic/Icarus_Verilog.pdf

讀VCD的好用軟體 - GTKWave

http://www.ptt.cc/bbs/Electronics/M.1251620125.A.3D1.html

[教學] Windows平台下使用開放軟件寫verilog

http://www.wretch.cc/blog/henry0714/11669422

icarus verilog

https://sites.google.com/site/verilog710/xiang-guan-gong-ju/icarus-verilog

Iverilog + Gtkwave + Notepad++的verilog環境

http://darkblack01.blogspot.tw/2012/10/iverilog-gtkwave-notepadverilog.html

沒有留言:

張貼留言